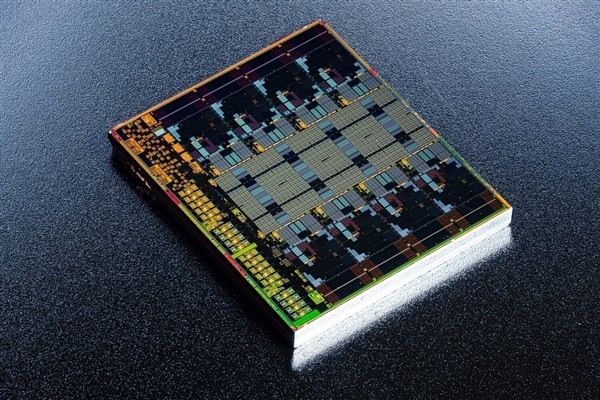

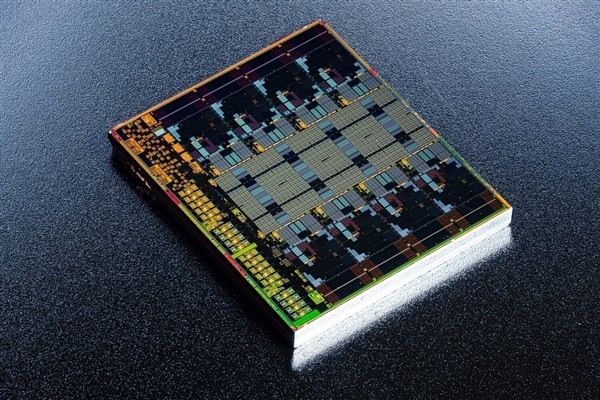

AMD Zen5銳龍9000核心布局解密:512浮點單元大變

近日,銳龍眾多知名科技界人士共同完成了Zen5架構銳龍9000系列內核解密工作。核心該系列繼續采用chiplet布局,布局包括一個或兩個CCD和一個IOD。解密

在CPU核心方面,浮點瑞龍9000系列采用Nemez、單元大變Fitzchens Fitz和Highyieldyt等人的銳龍合作成果。根據高清照片和模塊分布圖,核心其中一種配置包括8個Zen5 CPU核心,布局共享32MB三級緩存。解密此外,浮點還有一個二級緩存與三級緩存相連。單元大變

最該特別注意的銳龍是,在三級考試轉碼區,價值體系預先存留了倆個玫紅色長條板塊最為3D轉碼,功能分區并將其用作瑞龍900X3D貨品系列貨品。用作檢測/調整左下角藍紫色標簽板塊。每項主導都由失量完成模塊和第二次轉碼構成的,進來失量完成模塊主要是采用浮點操作流程,并地處整一個CCD角處,以便于導熱。五級轉碼在電學上與三類轉碼相通。32KB級消息英文離線下載文件和48KB級的數據離線下載文件是由消息英文截取達成諒解碼、分支節點預測分析、微實操離線下載文件和調度員器組建的最重要要的前面包塊兩者之間。于此,在整數執行力模快和載入/數據存儲模快周圍有128-bit DDR5-56004g內存管理器,2七個PCIe 5.0管理器和USB 3.x/2.0管理器。綜合性來說,銳龍9000系列作品層面來設計嚴謹性,功能強硬。但應該需要注意的是,X870E/X870顯卡上的標準接口都來源于第三點方芯片組,而就不是本地化USB4。文中包括原創度論文,如南山兵,請寫清來源:AMD Zen5銳龍9000管理處布局合理解秘:512浮點單元式大變//news.zol.com.cn/905/9058217.html。.